## L16: Power Dissipation in Digital Systems

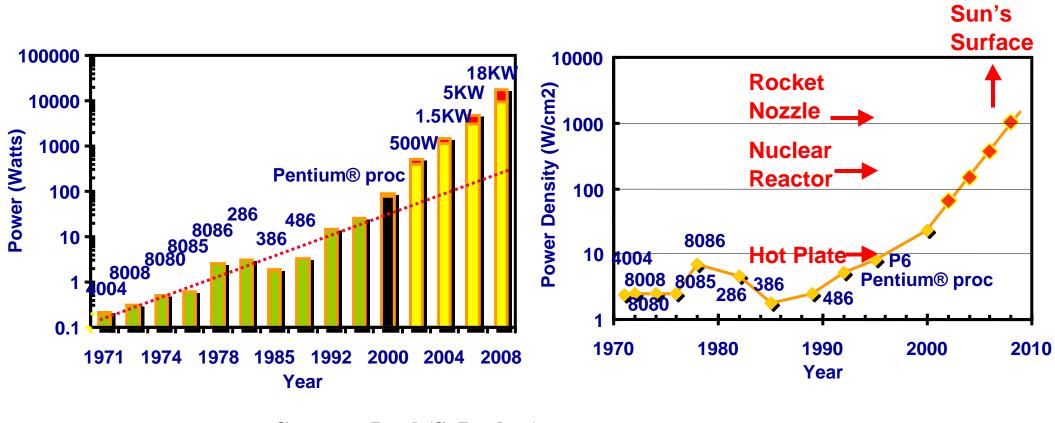

## **Problem #1: Power Dissipation/Heat**

**Courtesy Intel (S. Borkar)**

## How do you cool these chips??

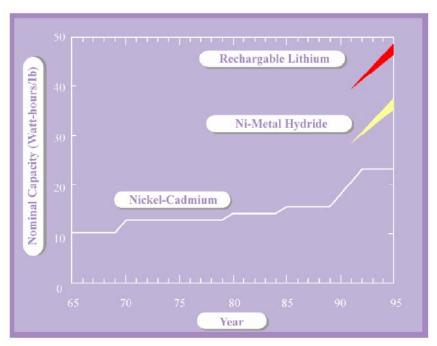

## **Problem #2: Energy Consumption**

(Image by MIT OCW. Adapted from Jon Eager, Gates Inc., S. Watanabe, Sony Inc.)

#### The Energy Problem

7.5 cm<sup>3</sup> AA battery

Alkaline: ~ 10,000J

## What can One Joule of energy do?

Mow your lawn for 1 ms

Operate a processor for ~ 7s

Send a 1 Megabyte file over 802.11b

Image by MIT OCW.

No Moore's law for batteries...

Today: Understand where power goes and ways to manage it

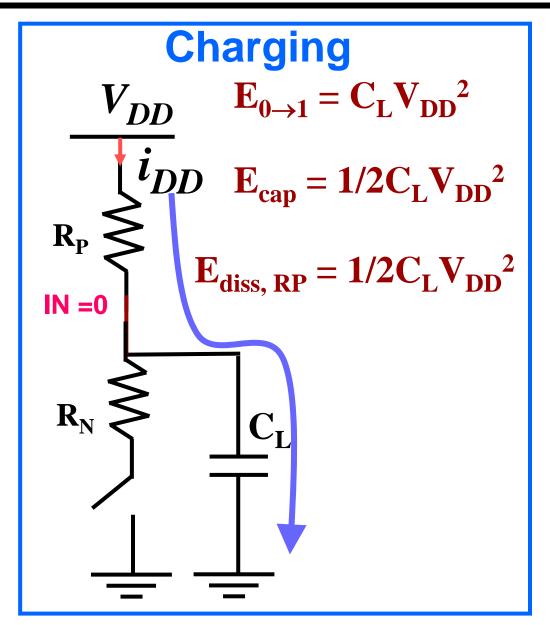

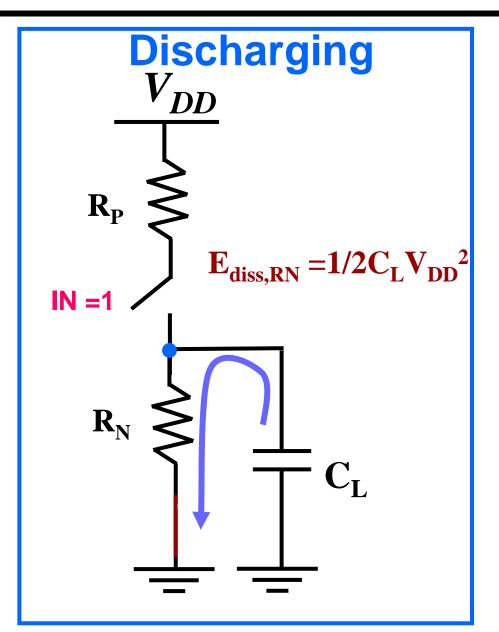

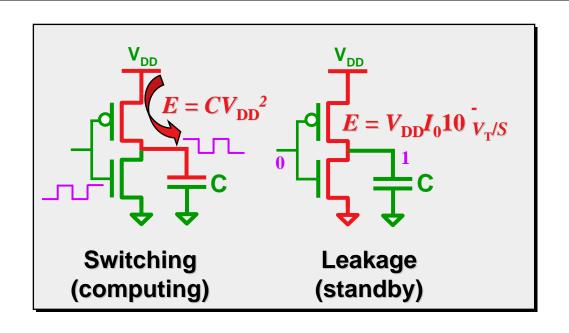

#### **Dynamic Energy Dissipation**

$$\mathbf{P} = \mathbf{C_L} \; \mathbf{V_{DD}}^2 f_{clk}$$

## The Transition Activity Factor $\alpha_{0->1}$

| Current<br>Input | Next<br>Input | Output<br>Transition |

|------------------|---------------|----------------------|

| 00               | 00            | 1 -> 1               |

| 00               | 01            | 1 -> 1               |

| 00               | 10            | 1 -> 1               |

| 00               | 11            | 1 -> 0               |

| 01               | 00            | 1 -> 1               |

| 01               | 01            | 1 -> 1               |

| 01               | 10            | 1 -> 1               |

| 01               | 11            | 1 -> 0               |

| 10               | 00            | 1 -> 1               |

| 10               | 01            | 1 -> 1               |

| 10               | 10            | 1 -> 1               |

| 10               | 11            | 1 -> 0               |

| 11               | 00            | 0 -> 1               |

| 11               | 01            | 0 -> 1               |

| 11               | 10            | 0 -> 1               |

| 11               | 11            | 0 -> 0               |

Assume inputs (A,B) arrive at f and are uniformly distributed

What is the average power dissipation?

$$\alpha_{0->1} = 3/16$$

$$\mathbf{P} = \alpha_{0->1} \mathbf{C_L} \mathbf{V_{DD}}^2 f$$

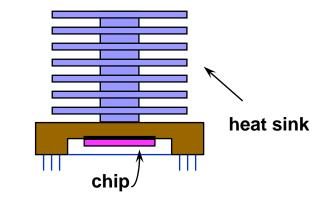

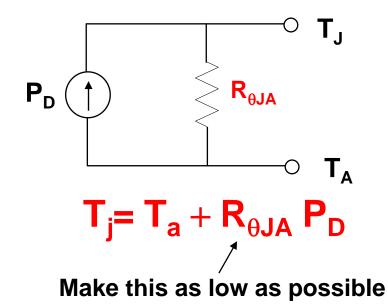

## **Junction (Silicon) Temperature**

#### Simple Scenario

$$T_j$$

- $T_a$ =  $R_{\theta JA} P_D$

$R_{\theta JA}$  is the thermal resistance between silicon and Ambient

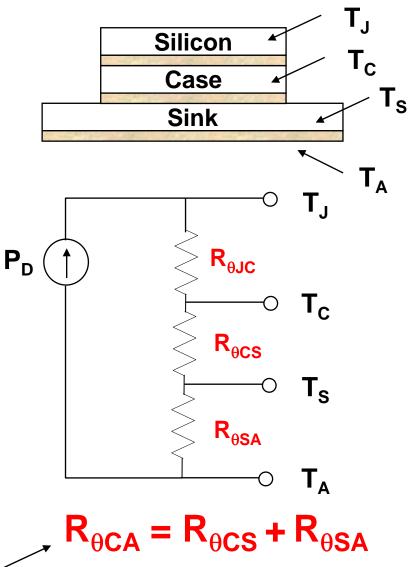

#### Realistic Scenario

is minimized by facilitating heat transfer (bolt case to extended metal surface – heat sink)

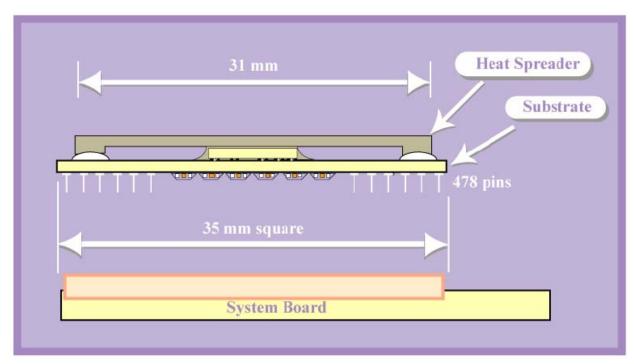

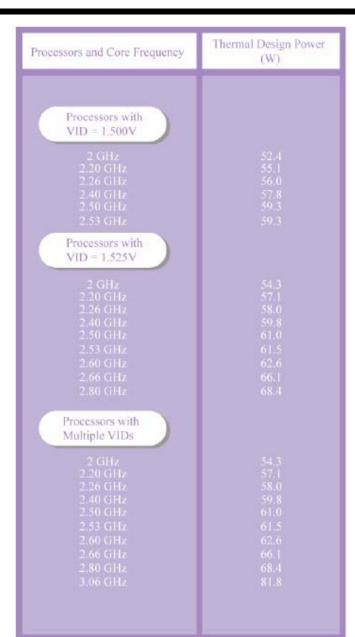

#### **Intel Pentium 4 Thermal Guidelines**

- Pentium 4 @ 3.06 GHz dissipates 81.8W!

- Maximum  $T_c = 69 \, ^{\circ}C$

- R<sub>CA</sub> < 0.23 °C/W for 50 C ambient</p>

- Typical chips dissipate 0.5-1W (cheap packages without forced air cooling)

Image by MIT OpenCourseWare.

Image by MIT OpenCourseWare. Adapted from Intel Pentium 4 documentation.

#### **Power Reduction Strategies**

$$\mathbf{P} = \alpha_{0->1} \ \mathbf{C_L} \ \mathbf{V_{DD}}^2 f$$

- Reduce Transition Activity or Switching Events

- Reduce Capacitance (e.g., keep wires short)

- Reduce Power Supply Voltage

- Frequency is typically fixed by the application, though this can be adjusted to control power

Optimize at all levels of design hierarchy

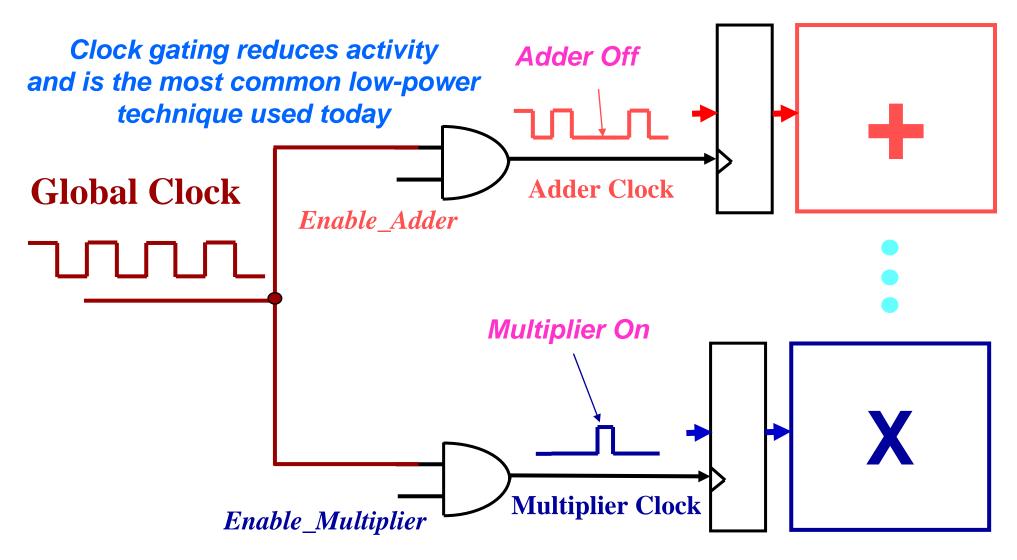

## **Clock Gating is a Good Idea!**

100's of different clocks in a microprocessor

#### Clock Gating Reduces Energy, does it reduce Power?

#### Does your GHz Processor run at a GHz?

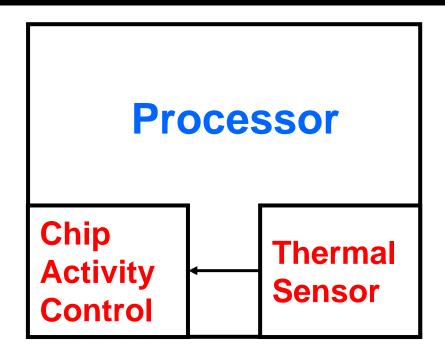

- Note that there is a difference between average and peak power

- On-chip thermal sensor (diode based), measures the silicon temperature

- If the silicon junction gets too hot (say 125 °C), then the activity is reduced (e.g., reduce clock rate or use clock gating)

#### **Use of Thermal Feedback**

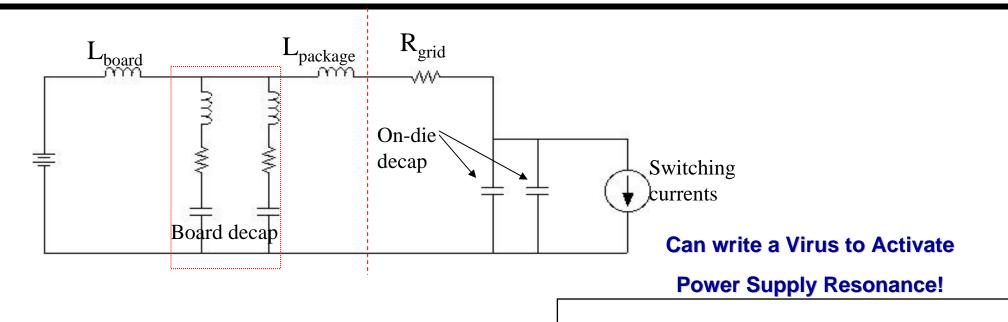

## **Power Supply Resonance**

Image removed due to copyright restrictions.

Image removed due to copyright restrictions.

Image removed due to copyright restrictions.

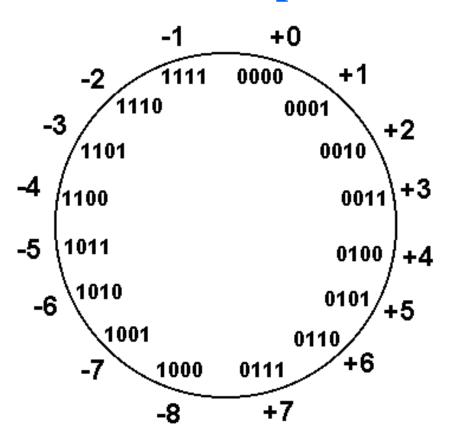

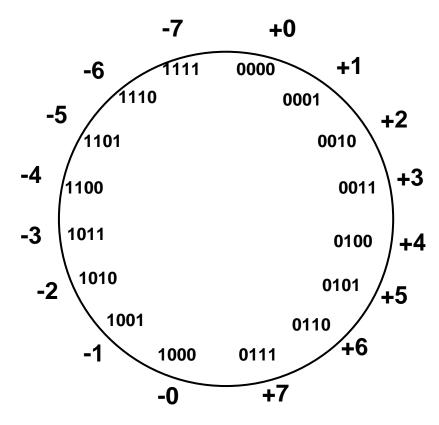

# Number Representation: Two's Complement vs. Sign Magnitude

#### Two's complement

#### Sign-Magnitude

Consider a 16 bit bus where inputs toggles between +1 and -1 (i.e., a small noise input) Which representation is more energy efficient?

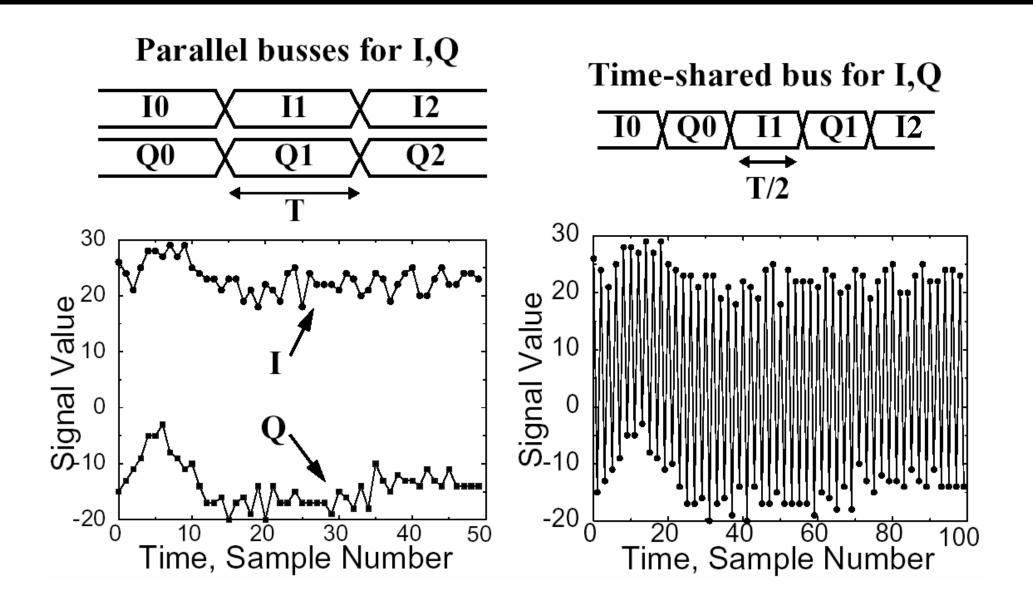

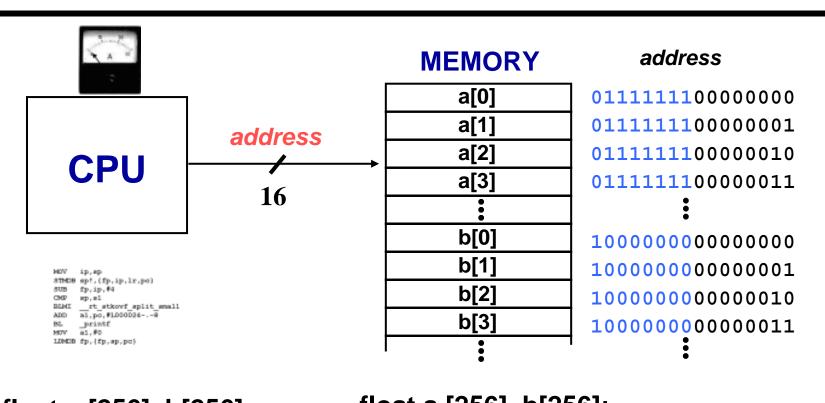

## Time Sharing is a Bad Idea

## Time Sharing Increases Switching Activity

#### IIII Not just a 6-1 Issue: "Cool" Software???

```

float a [256], b[256];

float a [256], b[256];

float pi = 3.14;

float pi = 3.14;

for (i = 0; i < 255; i++) \{a[i] = sin(pi * i /256);\}

for (i = 0; i < 255; i++) {

for (i = 0; i < 255; i++) \{b[i] = cos(pi * i /256);\}

a[i] = sin(pi * i /256);

b[i] = cos(pi * i /256);

```

512(8)+2+4+8+16+32+64+128+256

= 4607 bit transitions

2(8)+2(2+4+8+16+32+64+128+256)

= 1030 transitions

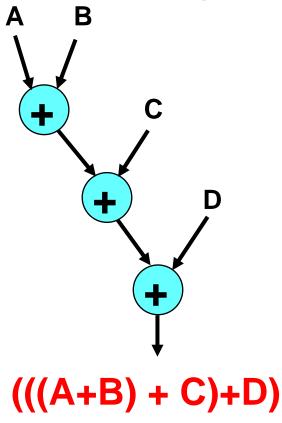

## **Glitching Transitions**

#### **Chain Topology**

#### **Tree Topology**

- Balancing paths reduces glitching transitions

- Structures such as multipliers have lot of glitching transitions

- Keeping logic depths short (e.g., pipelining) reduces glitching

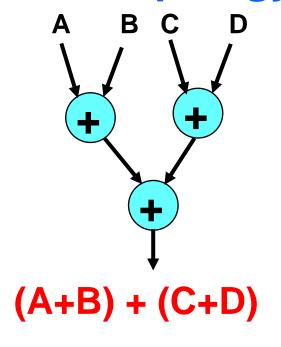

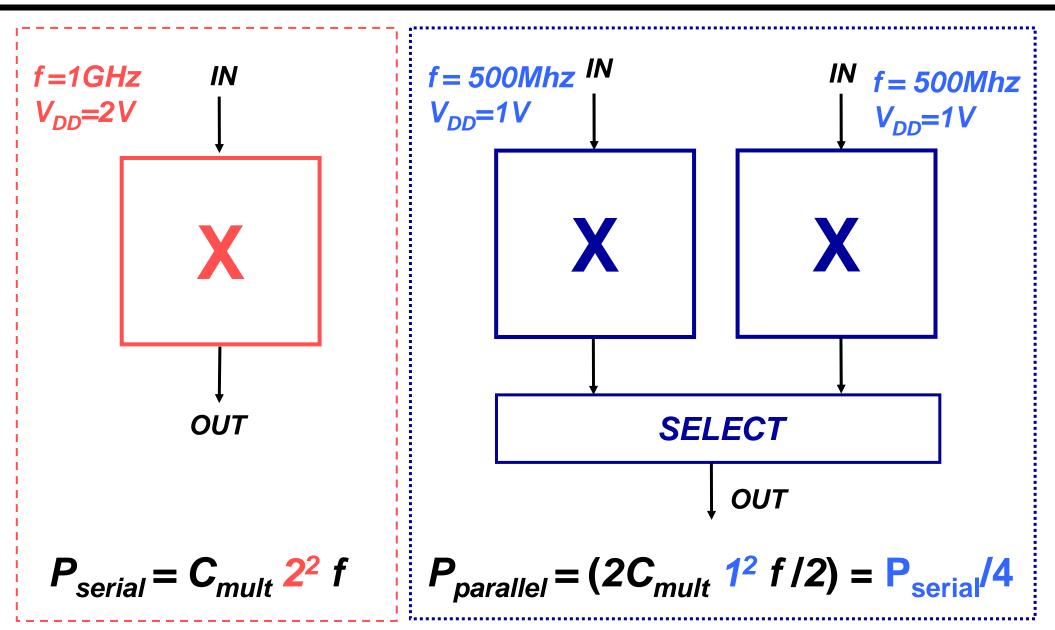

#### Reduce Supply Voltage: But is it Free?

$V_{DD}$  from 2V to 1V, energy  $\downarrow$  by x4, delay  $\uparrow$  x2

## Transistors Are Free... (What do you do with a Billion Transistors?)

#### **Trade Area for Low Power**

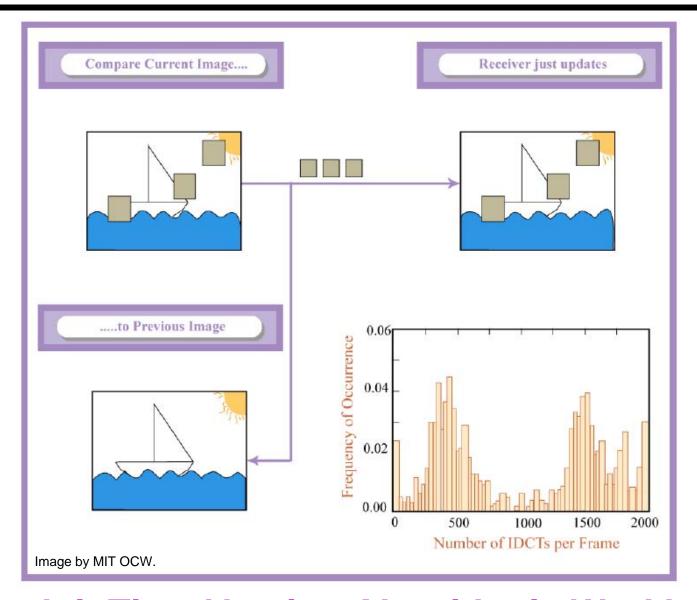

## **Algorithmic Workload**

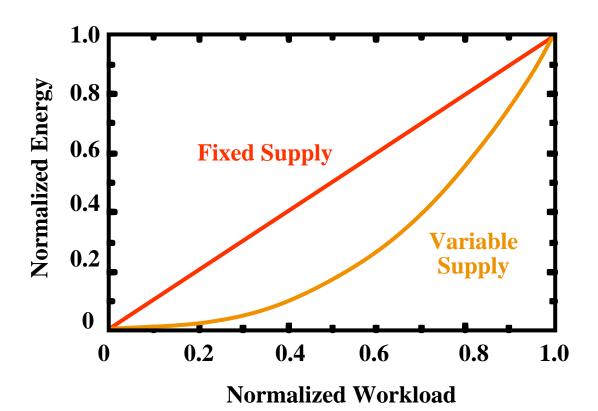

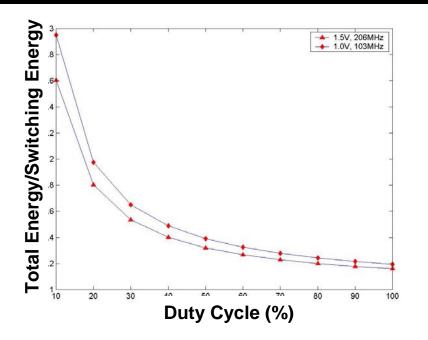

#### Exploit Time Varying Algorithmic Workload To Vary the Power Supply Voltage

#### **Dynamic Voltage Scaling (DVS)**

#### **Fixed Power Supply**

**ACTIVE**

**IDLE**

$$E_{FIXED} = \frac{1}{2} C V_{DD}^2$$

#### **Variable Power Supply**

#### **ACTIVE**

$$E_{VARIABLE} = \frac{1}{2} C (V_{DD}/2)^2 = E_{FIXED}/4$$

[Gutnik97]

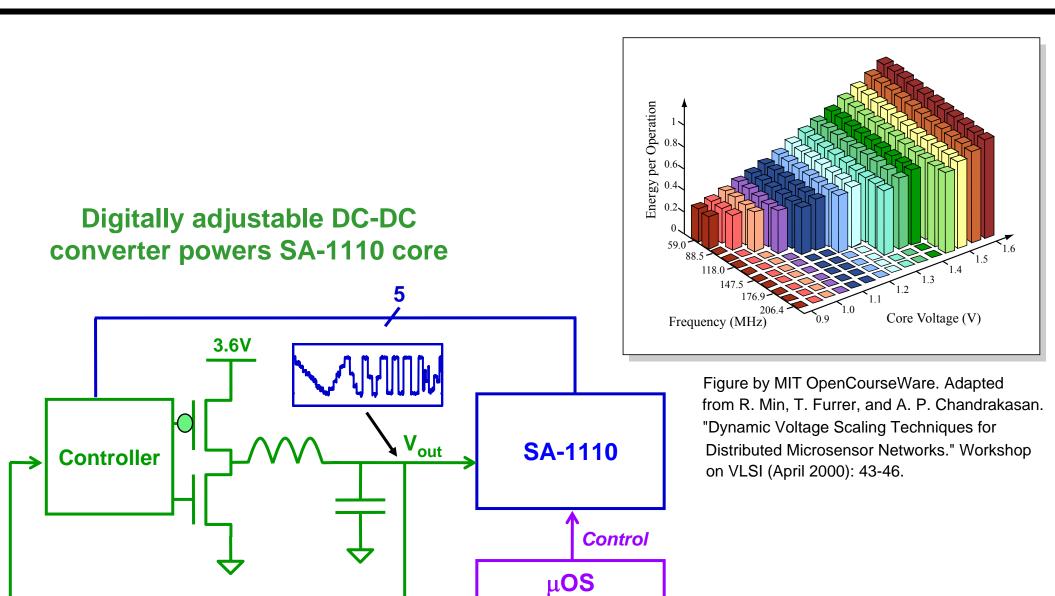

#### **DVS** on a Processor

μOS selects appropriate clock frequency based on workload and latency constraints

## **Energy Efficiency of Software**

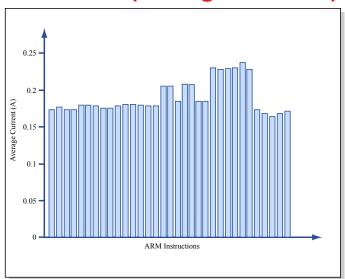

#### **Processor (StrongARM-1100)**

Figure by MIT OpenCourseWare. Adapted from A. Sinha, DAC.

Figure by MIT OpenCourseWare. Adapted from Montanaro 1996, JSSC.

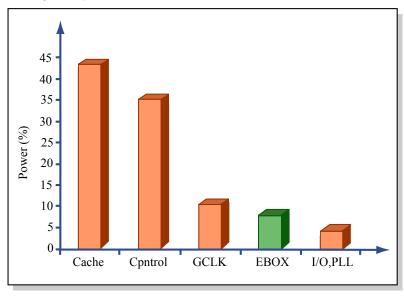

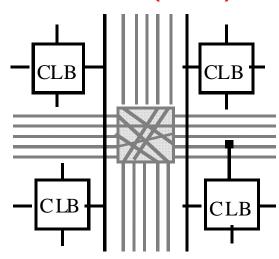

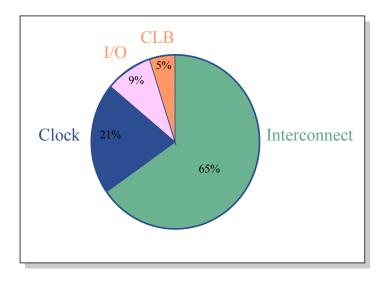

#### FPGA (Xilinx)

Image by MIT OpenCourseWare. Adapted from Kusse 1998, UCB.

#### "Software" Energy Dissipation has Large Overhead

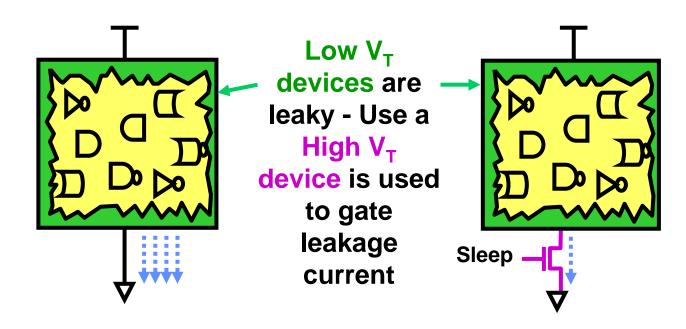

#### **Trends: Leakage and Power Gating**

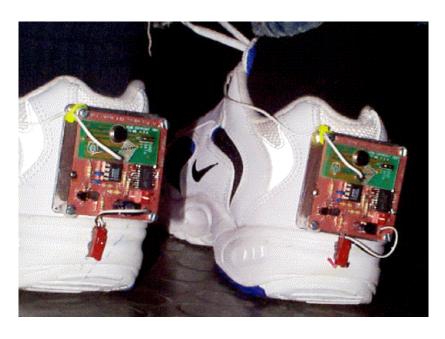

## **Trends: Energy Scavenging**

#### **MEMS Generator**

Image removed due to copyright restrictions.

#### **Power Harvesting Shoes**

Courtesy of Joe Paradiso (MIT Media Lab). Used with permission.

## Vibration-to-Electric Conversion

~ 10µW

After 3-6 steps, it provides 3 mA for 0.5 sec

~10mW